## EE105 Microelectronic Devices and Circuits: MOS Large Signal Model and Bias Circuits

Prof. Ming C. Wu

wu@eecs.berkeley.edu

511 Sutardja Dai Hall (SDH)

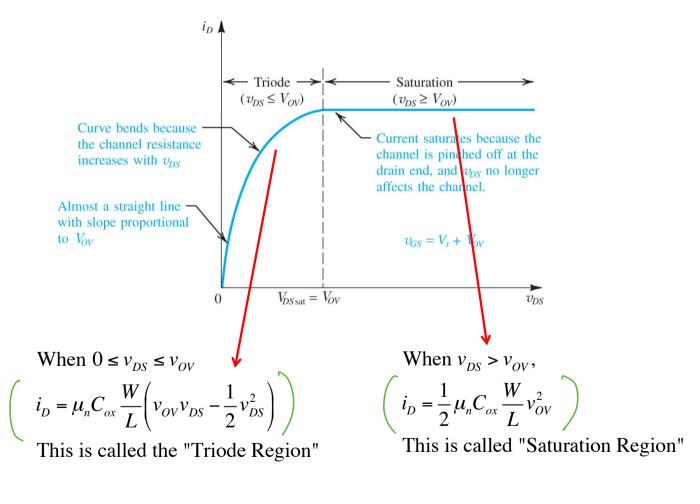

# **Saturation Region (v**<sub>DS</sub> > v<sub>OV</sub>)

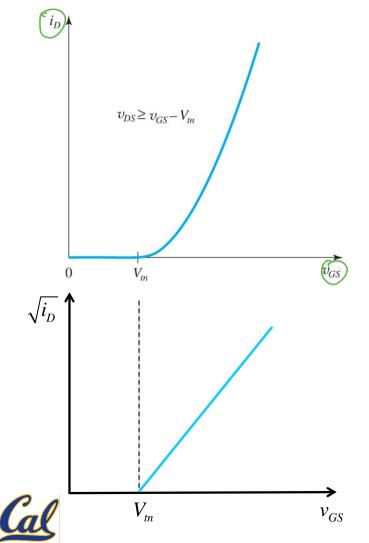

# **Drain Current vs Gate Voltage**

In Saturation Region

$$i_D = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} v_{OV}^2$$

$$= \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (v_{GS} - V_{tn})^2$$

To experimentally determine  $V_{tn}$ : Measure and plot  $\sqrt{i_D}$  versus  $v_{GS}$  $\sqrt{i_D} = \sqrt{\frac{1}{2}\mu_n C_{ox} \frac{W}{L}} (v_{GS} - V_{tn})$  $V_{tn}$  = intercept with horizontal axis

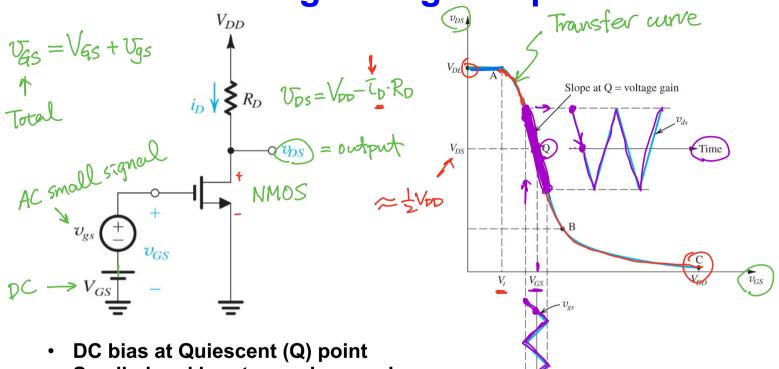

#### Analog Voltage Amplifier

- Small-signal input superimposed on a DC bias voltage

- Symbol used in this course:

$$v_{GS} = V_{GS} + v_{gs}$$

Need to know the transistor's I-V characteristics to find the voltage gain (and other properties of the amplifier)

Time

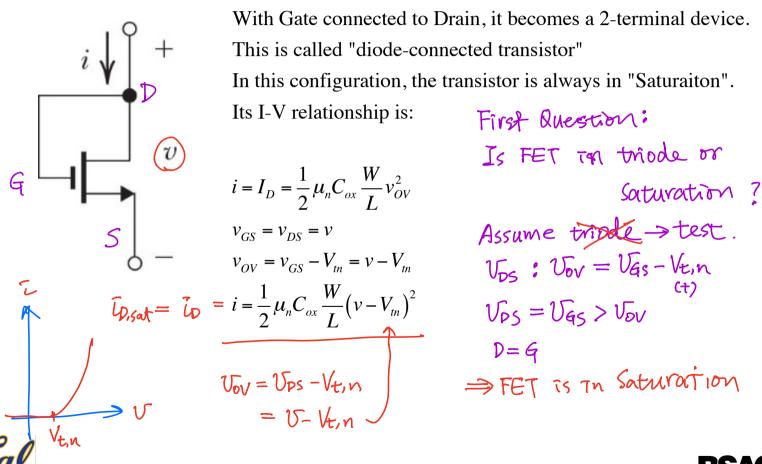

# **Diode-Connected Transistor**

**Example Circuit (1)**

Design Problem: Need set

$$J_{D}$$

.  $V_{DS}$

Determine  $R_s$  and  $R_D$  such that the NMOS is biased at  $I_D = 0.4mA$

and  $V_D = 0.5V$ . The NMOS has  $V_i = 0.7V$   $\mu_n C_{ox} = 100\mu A/V^2$ ,

$L = 1\mu m$  and  $W = 32\mu m$ .

$V_{DO} = 0.5V$ . The NMOS has  $V_i = 0.7V$   $\mu_n C_{ox} = 100\mu A/V^2$ ,

$L = 1\mu m$  and  $W = 32\mu m$ .

$V_{DO} = 0.5V$ .

$I_D = 0.4 wA = \frac{V_{DD} - V_D}{R_D}$

$R_D = \frac{V_{DD} - V_D}{I_D} = \frac{2.5 - 0.5}{0.4} = 5k\Omega$

$I_D = \frac{1}{2}\mu_n C_{ox} \frac{W}{L} (V_{OV}^2) = 0.4mA \rightarrow v_{OV} = 0.5V$

(channel length modulation can usually be ignored

when solving DC bias)

$v_{GS} = V_i + v_{OV} = 0.7 + 0.5 = 1.2V$

$R_D = \frac{V_S - V_{SS}}{I_D} = \frac{-1.2 - (-2.5)}{0.4} = 3.25k\Omega$

$R_S = \frac{(-2 - (-2.5))V}{0.4 wA}$

$R_S = \frac{(-2 - (-2.5))V}{0.4 wA}$